### Characterisation of 6T-SRAM

#### Sai Krishna Charan Dara(20171140)

March 2020

Sai Krishna Charan Dara(20171140)

Characterisation of 6T-SRAM

March 2020 1 / 11

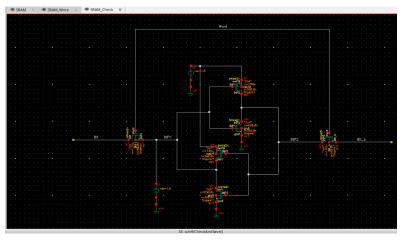

### Schematic of SRAM

6T-SRAM consists of 2 Inverters and 2 Access transistors.

Sai Krishna Charan Dara(20171140)

March 2020 2 / 11

Image: A math a math

- Assigned NMOS L= 360 nm W= 630 nm W/L=1.75.

- For good functionality of the circuit strength of transistors should be in following order.

- PULL DOWN Strength(D) > ACCESS Transistor(A) > PULL UP Strength(P).

- Hence my PMOS(PULL UP) W/L is 3 times the W/L of NMOS(PULL DOWN).W=1890 nm and L=360 nm.

- And ACCESS Transitor W/L is 2 times the W/L of NMOS(PULL DOWN).W=1260 nm and L=360 nm.

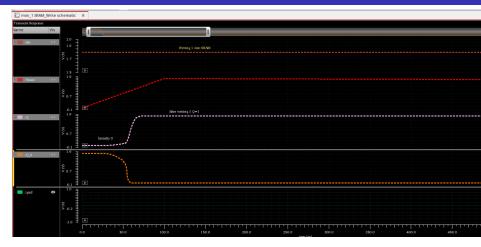

# Read Operation

- Initially 1 is stored. We need to read 1.

- Initially both Bit and Bit-bar are precharged to high.

- Itere we can see that Bit-bar decays to 0 representing 1 is stored.

Sai Krishna Charan Dara(20171140)

Characterisation of 6T-SRAM

Image: A math a math

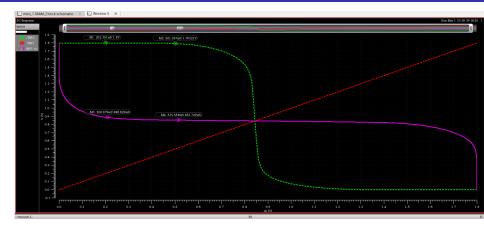

# Write Operation

- Initially 0 is stored in Q and 1 in Q-bar.

- Por writing we made Bit as 1 and Bit-bar as 0.

- We can see that after Word bit reaches 1, 1 is stored in Q and 0 in Q-bar.

Sai Krishna Charan Dara(20171140)

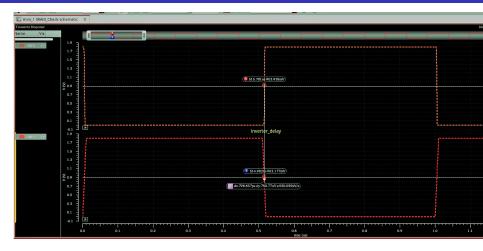

# Instantaneous Power at switching and steady state

- Here switching of Q happens from 0 to 1.

- 2 Switching instantaneous power is 468.23  $\mu W$ .

- Instantaneous power at steady state is 10.01564 pW.

Sai Krishna Charan Dara(20171140)

Characterisation of 6T-SRAM

#### Inverter Delay

Inverter Delay here measured between 50% of input to 50% of output.

Inverter Delay here is 798.657*ps*.

### Inverter Rise Time

- Inverter Rise here measured between 10% of maximum voltage and 90% of maximum voltage.

- Rise time here is 1.10298ns.

# Inverter Fall Time

- Inverter fall time here measured between 90% of maximum voltage and 10% of maximum voltage.

- Fall time here is 1.064ns.

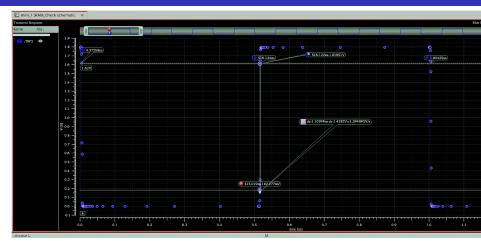

# Noise Margin of SRAM

- The noise margin is calculated as length of this square depicted by markers.

- Static Noise margin(SNM) =501.057 *mV*-202.351 *mV* = 298.706*mV*

# Thank you